코어 i7-12700KF와 코어 i9-12900KF 두 가지 CPU의 리뷰를 통해 인텔의 12세대 코어 CPU인 엘더 레이크가 11세대 대비 성능과 전성비가 대폭 강화된 것을 확인했다. 그렇다면 어떤 식으로 이러한 성능 개선을 이끌어 냈는지 궁금할 법도 한데, 이번 기사에서는 앞서 코어 i7-12700KF 리뷰 기사에서 예고했던 인텔 엘더 레이크 성능 향상의 비밀, 아키텍처 관련 내용을 정리하겠다.

빅-리틀의 핵심, 필요한 작업을 적절한 곳에 즉각 할당하는 스레드 디렉터

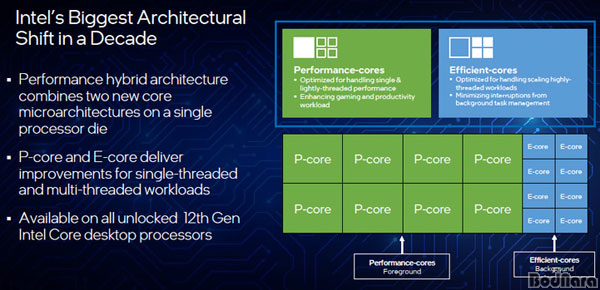

엘더 레이크가 빅-리틀로 나온다는 점이 제기된 이후 우려의 목소리가 나온 것은, 지금까지 동일한 아키텍처의 코어로만 구성되었던 x86 CPU 최초로 고성능 CPU 코어(P-코어)와 전력 효율을 위한 CPU 코어(E-코어)가 결합된 하이브리드 타입이라는데 있다.

웹서핑이나 워드프로세서 같이 높은 성능이 필요치 않은 성능이 필요없는 작업이라면 해당 작업이 어느 코어에 할당되어도 문제가 없지만, 랜더링이나 동영상 편집/ 변환 같이 높은 성능을 요구하는 작업이 E-코어에만 몰린다면 문제가 된다.

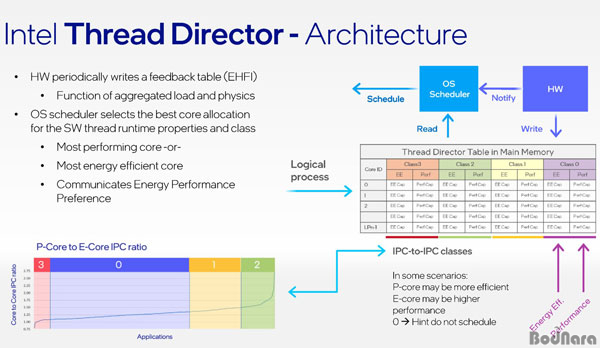

이에 인텔은 하드웨어 스케줄러인 스레드 디렉터를 통해 작업 유형에 어울리는 코어에 즉각 할당할 수 있도록 했다. 하드웨어 방식인 만큼 운영체제를 가리지 않지만, 최종적으로 작업을 할당하는 것은 운영체제 스케줄러의 역할인 만큼 OS 단에서도 대응이 이뤄져야한다. 그리고 엘더 레이크와 같은 x86 하이브리드 아키텍처 CPU에 최적회된 스케줄러를 지원하는 첫 OS가 바로 10월 5일 출시된 윈도우 11이다.

스레드 디렉터는 기본적으로 E-코어는 백그라운드 작업, P-코어는 포그라운드 작업에 할당하고, 성능과 전력 상태에 따라 크게 네 종류로 분류된 테이블 정보를 참고해 나노초 단위로 각 코어의 상태를 탐지, 작업별로 적합한 코어에 스레드를 할당하는 방식으로 동작한다.

이를 통해 각종 백그라운드 작업과 포그라운드 작업이 수시 전환되는데다 On/ Off 되는 복잡한 PC 구동 환경에서 최적의 성능과 소비전력을 구현할 수 있게 제어한다. 물론, 스레드 디렉터는 코어의 상태 감지와 스레드 할당을 수행하지만, 실제 이를 최종 조율하는 곳은 운영체제의 스케줄러다.

따라서 운영체제 스케줄러가 인텔 엘더 레이크의 하이브리드 아키텍처를 제대로 지원하는 것이 성능을 제대로 활용하는데 있어 중요한 요인 중 하나이며, 현 시점에서 인텔 엘더 레이크의 하이브리드 아키텍처를 정식 지원하는 운영체제는 지난 10월 5일 출시된 윈도우 11이 유일하다.

한편, 스레드 디렉터는 자동으로 적절한 코어와 스레드에 작업을 할당하지만, 인텔은 개발자들을 위해 크게 세 가지 최적화 방식을 제안한다.

첫째는 자체적으로 P-코어와 E-코어에 작업을 할당하도록 두는 것이다. 경우에 따라 워크로드가 적절하지 않은 코어에 할당될 수 있어, 인텔은 어플리케이션의 스레드 관리에 대해 아래 두 가지 중 한 가지 경우를 고려하도록 권한다.

두 번째는 고성능이 요구되는 주요 워크로드의 우선순위를 높여 P-코어에 할당, 백그라운드 작업의 우선 순위는 '보통' 미만으로 낮추고 필요하다면 E-코어에 할당해 성능을 우선 하는 것.

마지막으로 스레드 풀을 P-코어 할당과 E-코어 배정으로 구분해 성능과 효율을 모두 노리는 것으로, 두 번째 최적화에 대해서는 'Good', 마지막 최적화에 대해 'Best' 시나리오로 분류해, 두 번째 최적화의 경우 일부 백그라운드 작업이 P-코어에 할당될 수 있는 경우도 방지하도록 권한다.

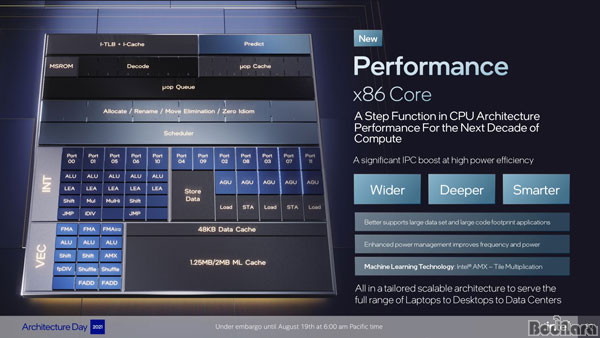

넓고, 깊게, 스마트한 처리, 골든 코브 P-코어 아키텍처

인텔은 지난 2018년, 6세대 코어 CPU 부터 적용해온 '레이크' 시리즈의 후속 CPU 아키텍처인 '서니 코브'를 발표했고, 아이스 레이크를 포함한 모바일 프로세서에 우선 적용해왔다. 모바일 타이거 레이크에 적용된 '윌로우 코브' 아키텍처의 14nm 백포팅 아키텍처인 '사이프레스 코브(Cypress Cove) 아키텍처가 데스크탑용 11세대 코어 CPU인 로켓 레이크에 적용된데 이어, 12세대 코어 CPU에서는 모바일 플랫폼을 동시에 아우르는 골든 코브 아키텍처가 P-코어에 사용되었다.

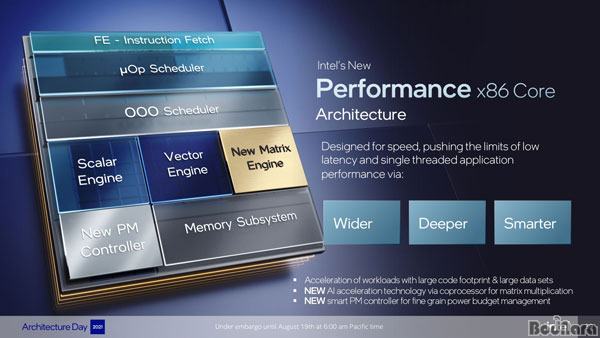

골든 코브 아키텍처는 서니 코브와 마찬가지로 넓게(Wider), 깊게(Deeper), 스마트하게(Smarter)의 세 가지에 집중하면서, 속도와 레이턴시 및 싱글 스레드 어플리케이션의 성능 개선에 집중한 것이 특징이다. 실제로 코어 i7-12700KF 테스트 결과를 보면 싱글 스레드 성능이 대폭 개선된 것을 확인할 수 있었다.

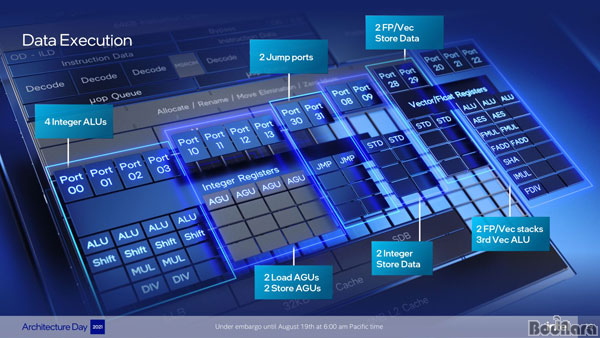

엘더 레이크의 P-코어에 적용된 골든 코브 아키텍처는 기본적으로 비순차 실행 스케줄러와 버터, 물리 레지스터를 활장하며, 할당창(Allocation Window)를 넓히고, 더 많은 실행 포트를 제공하는 것이 특징이다.

여기에 더 스마트해진 분기 예측을 통해 병렬화 수준 및 선응을 높였고, 코어별로 전력 제어 컨트롤러를 내장해 마이크로초 단위로 전력 상태를 탐지/ 제어해 각 어플리케이션에 최적화된 전력 공급 및 더 빨라진 평균 클럭 구현이 가능해진다.

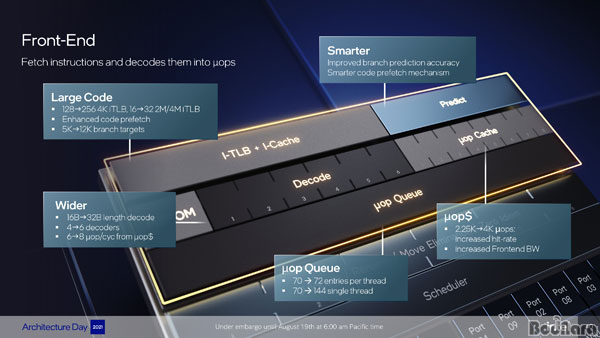

보다 세부적으로 들어가면 디코더는 4개에서 6개로, 마이크로op 캐시 피드는 사이클당 6에서 8로 늘었고, 이에 따라 사이틀당 명령어 패치(fetch) 용량이 16byte에서 32byte로 두 배 늘었고, 마이크로op 캐시도 2.25K에서 4K 엔트리로 확장되었다.

마이크로op 큐도 스레드당 70에서 72엔트리로 확장, 싱글 스레드시 최대 144엔트리를 지원하면서 비순차 실행 엔진의 속도를 높이고 마이크로op 적중률도 개선했다.

4K iTLB((instruction Translation Look-aside Buffers)는 128에서 256로, 분기 타겟도 5K에서 12K로 대폭 강화했다. 분기 점프 오예측을 줄이기 위해 분기 예측을 개선하고 BTB(Branch Target Buffe)도 두 배 이상으로 개선했다.

한편, 비순차 실행 엔진은 배치 유닛을 5개에서 6개로, 실행 포트는 10개에서 12개로 늘리고, 항목 재정렬 버퍼도 352에서 512로 크게 늘렸다. 이를 통해 리네이밍/ 배치 등 일부 간단한 명령 실행시 종속성 체인을 축소, 깊은 파이프라인에서 투입되는 리소스를 줄이고 다른 동작을 더욱 빠르게 실행하고 절전 효과를 기대할 수 있다.

정수 및 벡터 실행 유닛과 관련해서는 ALU와 LEA가 포함된 다섯 번째 정수 실행 유닛이 추가되었고, 벡터 관련, 1번과 5번 포트에 FADD(Fast ADDers)를 추가하고, FMA에는 AVX512기반 FP16 연산을 지원하도록 개선했지만, 아쉽게도 엘더 레이크에서는 사용되지 않는다.

코어당 캐시 용량은 L1 데이터 캐시 48KB, L1 명령어 캐시 32KB로 유지되었지만, L2 캐시는 512KB에서 1.25MB로 두 배 이상 증가했으며, L3 캐시 용량도 코어당 2MB에서 2.5MB꼴로 확대 되었다.

단순 용량 확장 뿐 아니라 L1 캐시 로드 포트는 2에서 3으로, L1D 캐시의 페이지 워커는 2에서 4로, L1D TLB는 50% 늘리면서 더 높은 수준의 병렬화를 구현했다. 캐시 용량 증설은 레이턴시 증가를 가져오지만, 새로운 프리페치 엔진을 통해 구동중인 프로그램의 잠재적 메모리 엑세스 패턴을 특정해 잠재적 경로를 프리패치해 대응할 수 있음을 알렸다.

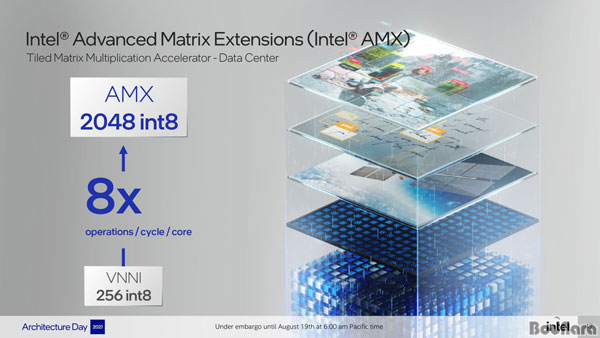

한편, 엘더 레이크 P-코어에서는 지원되지 않지만, 골든 코브 아키텍처에는 AMX(Advanced Matrix Extensions)을 지원한다. 데이터센터 AI 지원을 위한 행렬 연산 가속용 명령어로, 추론과 기계학습 등에 뛰어난 VNNII 대비 8배의 처리 성능을 제공할 수 있다고 소개되었는데, 인텔의 차세대 제온 스케일러블 프로세서인 코드네임 사파이어 레피즈에서 만날 수 있게될 것이다.

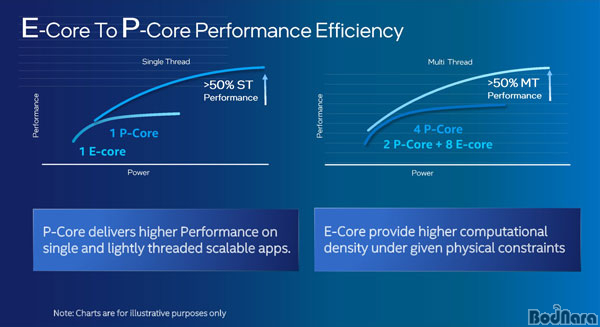

전력 효율 우선, 그레이스몬트 아키텍처 E-코어

주로 백그라운드 작업 처리에 우선 할당되는 E-코어는 특성상 P-코어보다 낮은 성능을 발휘하지만, 그래도 스카이레이크 코어 대비 동일 전력에서 40% 높은 성능을 발휘하고, 동일 성능이라면 전력 소모를 40%낮춘 코어다.

엘더 레이크의 E-코어 4개가 결합된 모듈은 스카이레이크 1코어급의 작은 크기로 설계되었으며, 동일 전력 조건일 경우 스카이레이크 1코어 2스레드 대비 엘더 레이크 E-코어 4개 모듈이 80% 더 높은 성능을 발휘한다.

인텔 엘더 레이크 E-코어의 그레이스몬트 아키텍처는 5천 분기 타겟 캐시 스위칭을 통해 분기 예측 정확도를 높인다. 인텔에 따르면 이러한 긴 기록(history) 기반 분기 예측 시스템은 명령어 포인터의 정확성을 높이는데 도움을 주며, 결과적으로 명령어 캐시 미스 상태가 프로그램 실행에 치명적인 수준에 도달하기 전 발견하고 수정할 수 있게 해준다.

프론트 엔드의 L1 명령어 캐시를 P-코어의 32KB 대비 두 배에 달하는 64KB 용량을 배치해 보다 명령어를 밀접하게 관리해 전력 제한을 유도하는 한편, 인텔 최초의 주문형 명령 길이 디코더를 탑재했다.

해당 디코더는 명령어 캐시와 함께 저장되는 사전 디코딩 정보를 생성, 앞선 명령어의 기록을 제공해 익숙한 코드가 길이 디코더를 우회해 에너지 절약에 기여한다. 비순차실행 디코더는 듀얼 3와이드 디코더으로 클러스터화되어 사이클당 최대 여섯 개의 명령어를 디코딩할 수 있으며, 병렬 처리를 위해 하드웨어 기반 로드 밸런싱이 지원된다.

백엔드 단에서는 256 엔트리 비순차 윈도우와 5-와이드 어로케이션, 8-와이드 리타이어 구성으로 17 실행 포트에 연결되며, 이러한 구성은 일부 전력 상태에서 스카이레이크보다 높은 정수 IPC를 제공한다.

또한 사이클 당 2개의 분기를 해결할 수 있는 듀얼 정수 승수 및 분배기를 갖춘 4개의 일반 정수 실행 포트를 갖췄고, VNNI 명령어에 사용되는 정수 승수(integer multiplier)를 갖춘 SIMD ALU도 세 개나 갖췄다.

두 개의 대칭 부동 소수점 파이프라인은 두 개의 독립적인 더하기 및 곱 연산을 수행할 수 있고, 벡터 확장을 통해 사이클당 두 개의 FP 곱연산 및 더하기 연산을 수행할 수 있다. 2개의 AE 및 1개의 SHA 가속 엔진도 갖췄다.

메모리 시스템은 동시에 32KB 읽기/ 쓰기가 가능한 듀얼 로드/ 스토어 파이프라인을 갖추고 있으며, 코어별 L2 캐시가 할당된 P-코어와 달리 E-코어의 L2 캐시는 4개 코어의 통합형으로 2MB를 제공한다.

E-코어의 L2 캐시는 코어당 1MB꼴로 P-코어의 1.25MB보다 용량면에서 적은 것을 알 수 있다. 17사이클 레이턴시에서 사이클당 64byte의 대역폭을 제공하며, 코어와 서로 다른 소프트웨어 스레드간 리소스를 공정하게 분배하는 리소스 디렉터 기술도 도입되었다.

한편, 그레이스몬트 아키텍처 E-코어의 L2 캐시는 최대 4MB 구성이 가능한데, 일반 소비자용 엘더 레이크는 2MB가 제공되며, L2 캐시 4MB는 서버나 데이터센터용 코어에 탑재될 예정이다.

기사 및 더 읽기 ( 빅-리틀 인텔 엘더 레이크, 성능 향상의 열쇠 아키텍처는? : 기사 - 아이폰, 갤럭시S, 안드로이드 스마트폰을 위한 보드나라 모바일 - 보드나라 )https://ift.tt/3bKTA31

과학/기술

Bagikan Berita Ini

0 Response to "빅-리틀 인텔 엘더 레이크, 성능 향상의 열쇠 아키텍처는? : 기사 - 아이폰, 갤럭시S, 안드로이드 스마트폰을 위한 보드나라 모바일 - 보드나라"

Post a Comment